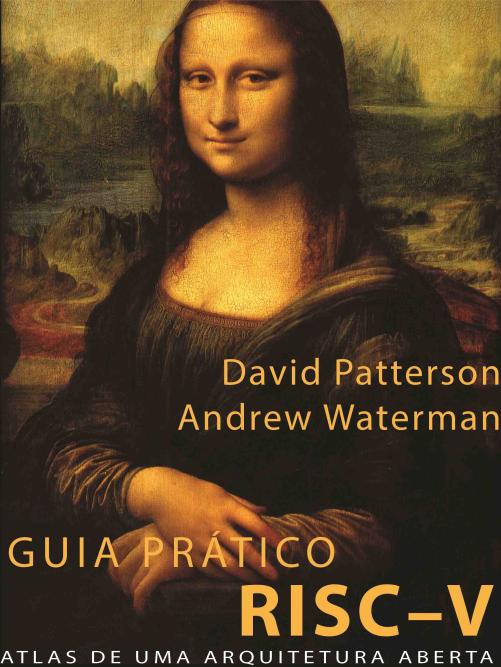

Sobre o Livro

O Guia Prático RISC-V é uma consisa introdução e referência para programadores de sistemas embarcados, estudantes, e aos curiosos sobre um arquitetura moderna, popular e aberta. O RISC-V abrange desde o microcontrolador de 32 bits de baixo custo até o mais rápido computador na nuvem de 64 bits. Dez capítulos apresentam cada componente do conjunto de instruções modular RISC-V, muitas vezes contrastando o código compilado de C para RISC-V versus arquiteturas ARM, Intel x86 e MIPS, porém, os leitores podem iniciar a programação logo após o Capítulo 2.

Introduz o RISC-V em apenas 100 páginas, incluindo 75 figuras

Cartão de Referência de 2 páginas com o resumo de todas instruções

Glossário de Instruções de 50 páginas que define todas instruções detalhadamente

75 dicas de boas práticas de projeto de arquitetura

50 barras laterais com comentários interessantes a respeito do histórico do RISC-V

25 citações para transmitir o conhecimento de cientistas e engenheiros notáveis